| Haute précision |  |

| Petite taille | |

| Vitesse de suivi élevée | |

| Suivi ininterrompu pendant le transfert de données | |

| Sortie de verrouillage à trois états | |

| Faible consommation d'énergie |

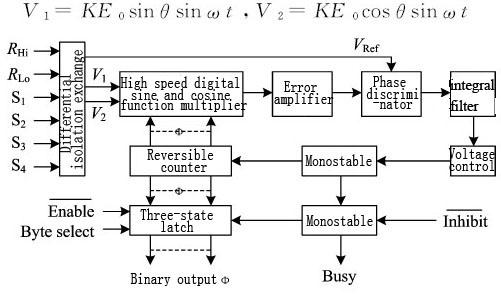

le signal de sortie est un code binaire naturel parallèle mis en mémoire tampon à travers | verrou à trois états et compatible avec le niveau TTL. |

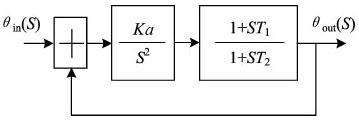

Le produit applique un circuit servo de second ordre de petite taille et léger | |

poids, et l'utilisateur peut l'utiliser très facilement en contrôlant | |

broches de signalisation. | |

Tableau 2 Conditions nominales et conditions de fonctionnement recommandées | Max. valeur de notation absolue |

Tension d'alimentation +VS : 12,5 ~ 17,5 V | |

Tension d'alimentation -VS : -17,5 ~ -12,5 V | |

Tension logique VL : 7V | |

Plage de température de stockage : -40~+100℃ | |

Conditions de fonctionnement recommandées |

Tension de référence (valeur efficace) VRef : valeur nominale ±10 % | Tension du signal (valeur efficace) V1* : valeur nominale ±10 % Fréquence de référence f* : valeur nominale ±10 % | Plage de température de fonctionnement TA : -40 ~ + 85 ℃ | Remarque : * indique qu'il peut être personnalisé selon les besoins de l'utilisateur. | |

Tableau 2 Caractéristiques électriques | Paramètre | |||

Conditions (-40~+85℃) | (Sauf indication contraire) | 12 | 16 | (séries MSDC/MRDC37) |

Unité | – | 3 | 36 | Min. |

Max. | Résolution/RES | Gamme de 0~360º | – | V |

Bit | Vitesse de suivi/St① | – | RPS | V |

Haut niveau de sortie/VOH | TAu003d25℃ | – | 2.4 | W |

Faible niveau de sortie/VOL | TAu003d25℃ | – | 0,8 | % |

Consommation d'énergie/DP | – | 2 | TAu003d25℃ | V |

1.3 | – | 2 | 90 | V |

Linéarité Vel/ERl | – | 30 | TAu003d25℃ | Hz |

1.0 | – | ±3 | Plage de tension de référence | 115 |

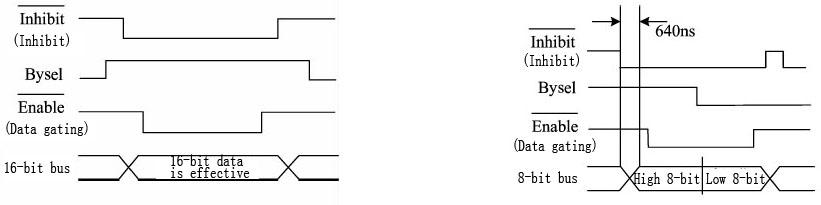

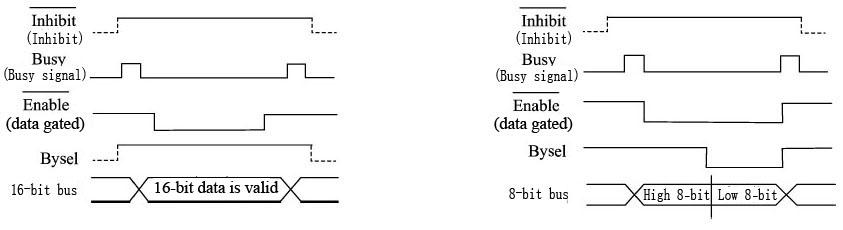

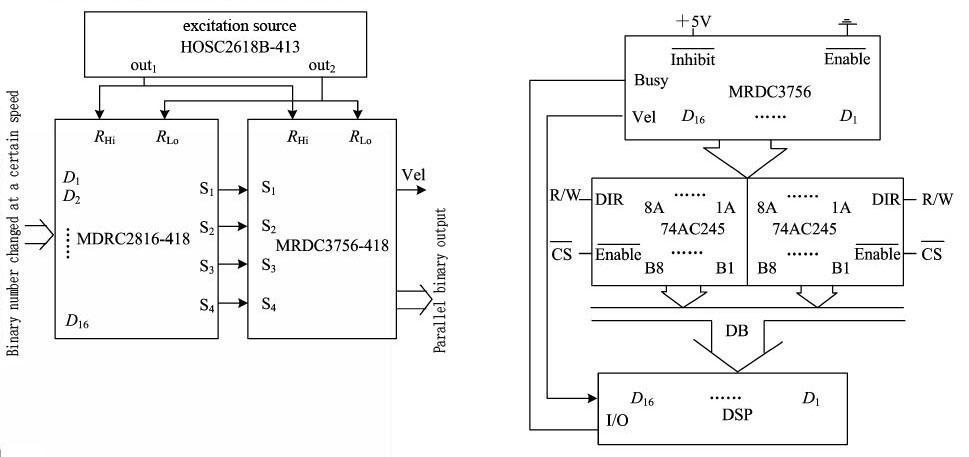

B: le convertisseur est connecté au bus 8 bits, les bits D1 ~ D8 sont connectés au bus de données et les autres sont vides. | Réglez l'inhibition de la logique 1 à la logique 0 (verrouillage des données) et attendez 1 μs ; réglez Enable sur 0 logique pour permettre au verrou du convertisseur de sortir des données ; Positionner | Bysel à la logique 1, lisez directement les données 8 bits élevées, réglez Bysel sur | logique 0, lire les données dans d'autres bits avec un remplissage automatique par zéro dans | les morceaux vacants ; mis à la logique 1 afin de se préparer à lire les prochaines données effectives (Fig. 5). | Inhiber | Fig4 Séquence temporelle du transfert de bus 16 bits Fig5 Séquence temporelle du transfert de bus 8 bits | (2) Méthode Busy (lecture asynchrone) : | En lecture asynchrone, est défini Inhibit sur 1 logique ou vide, que la boucle interne soit toujours dans le |

1 | D1 | l'état stable ou si les données de sortie sont valides doivent être déterminés | 13 | par l'état du signal occupé Occupé. Lorsque le signal occupé est au niveau haut | niveau, il indique que les données sont en cours de conversion, et les données à ce | 25 | le temps est instable et invalide ; lorsque le signal d'occupation est au niveau bas, il | indique que la conversion des données est terminée et que les données à ce stade |

2 | D2 | le temps est stable et valide. Une fois que le niveau haut apparaît dans Occupé pendant la lecture, | 14 | la lecture à ce moment est invalide. En mode de lecture asynchrone, le | La sortie occupée est un train d'impulsions de niveau TTL, sa largeur dépend de son | 26 | vitesse de rotation, il existe également deux méthodes d'utilisation du bus, c'est-à-dire 8 bits | et 16 bits, la lecture des données pendant la sortie effective des données est également |

3 | D3 | commandé par Activer , veuillez vous référer au diagramme de séquence de temps pour le transfert de données (Fig. 6 et Fig. 7). | 15 | Fig.6 Diagramme de séquence temporelle pour le transfert de bus 16 bits Fig.7 Diagramme de séquence temporelle pour le transfert de bus 8 bits | Broches de signal d'état : Occupé, DIR, R, C. | 27 | Lorsque l'entrée du convertisseur change, Busy émet un train d'impulsions | du niveau CMOS, sa fréquence est déterminée par la rotation la plus élevée |

4 | D4 | la vitesse. Lorsque Busy est au niveau haut, cela signifie que le servo de second ordre | 16 | circuit dans le convertisseur fonctionne, les données à l'extrémité de sortie numérique sont | en changeant; au contraire, l'ordinateur peut directement lire les données. | 28 | Le signal DIR est utilisé pour indiquer la rotation avant/arrière. Lorsque la sortie | |

5 | D5 | le code est compté, la sortie est de haut niveau ; lorsque le code de sortie est | 17 | NC | compte à rebours, la sortie est de niveau bas. | 29 | Sortie de signal zéro R.C : lorsque les données de sortie incrémentent de 1 à | tous 0, ou les données de sortie décrémentent de tous 0 à tous 1, le |

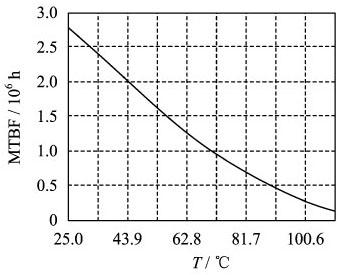

6 | D6 | la sortie est une impulsion positive, la largeur d'impulsion est de 200 μs. | 18 | 5. Courbe MTBF des convertisseurs synchro-numériques ou des convertisseurs résolveur-numérique (séries MSDC/MRDC37) (Fig. 7) | Fig. 8 Courbe de température MTBF | 30 | (Remarque : selon GJB/Z299B-98, bon état du sol envisagé) | |

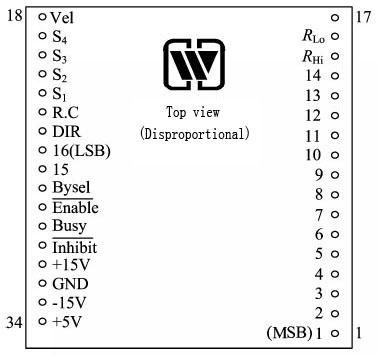

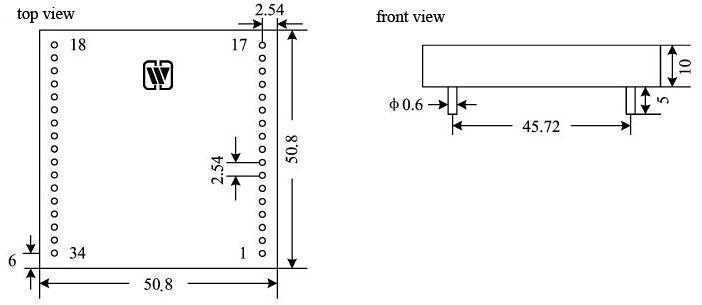

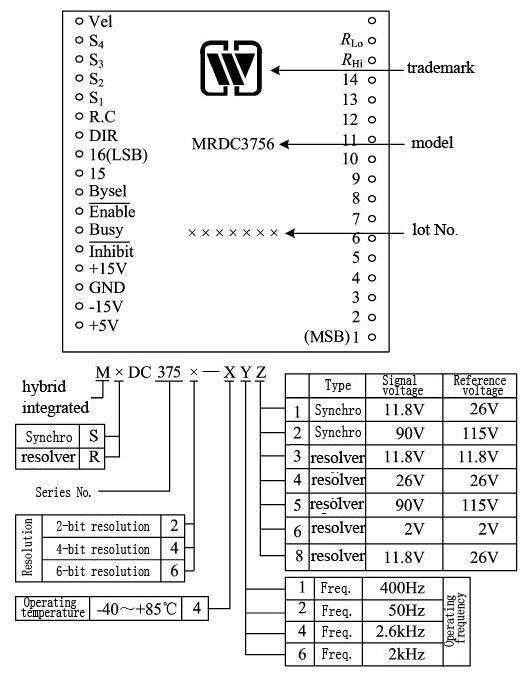

7 | D7 | 6. Désignation des broches des convertisseurs synchro-numériques ou des convertisseurs résolveur-numérique (séries MSDC/MRDC37) (Fig. 9, tableau 3) | 19 | S4 | Fig.9 Désignation de la broche (vue de dessus) | 31 | Tableau 3 Désignation de la broche | Broche |

8 | D8 | Symbole | 20 | S3 | Sens | 32 | Broche | Symbole |

9 | D9 | Sens | 21 | S2 | Broche | 33 | Symbole | Sens |

10 | Sortie numérique 1 (bit le plus élevé) | D13 | 22 | S1 | Sortie numérique 13 | 34 | VL | D16 |

11 | Sortie numérique 16 | Sortie numérique 2 | 23 | D14 | Sortie numérique 14 | |||

12 | D15 | Sortie numérique 15 | 24 | Sortie numérique 3 | RHi |

Entrée de signal de référence (bas de gamme) | Activer le signal | Sortie numérique 5 | Impasse | Occupé | Signal occupé |

Sortie numérique 6 | Vel | 7 | Sortie de tension de vitesse | 13 | Signal d'inhibition |

2 | Sortie numérique 7 | 8 | Entrée de signaux | 14 | +Vs |

3 | Alimentation +15V | 9 | Sortie numérique 8 | 15 | Entrée de signaux |

4 | Terre | 10 | Terre d'alimentation | 16 | Sortie numérique 9 |

5 | Entrée de signaux | 11 | -Vs | ||

6 | -Alimentation 15V | 12 | D10 |

| |

| Entrée de signaux | Alimentation +5V |

X

X