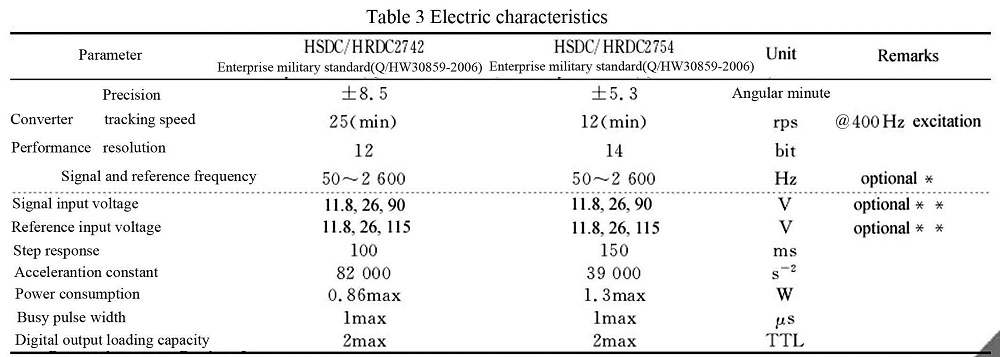

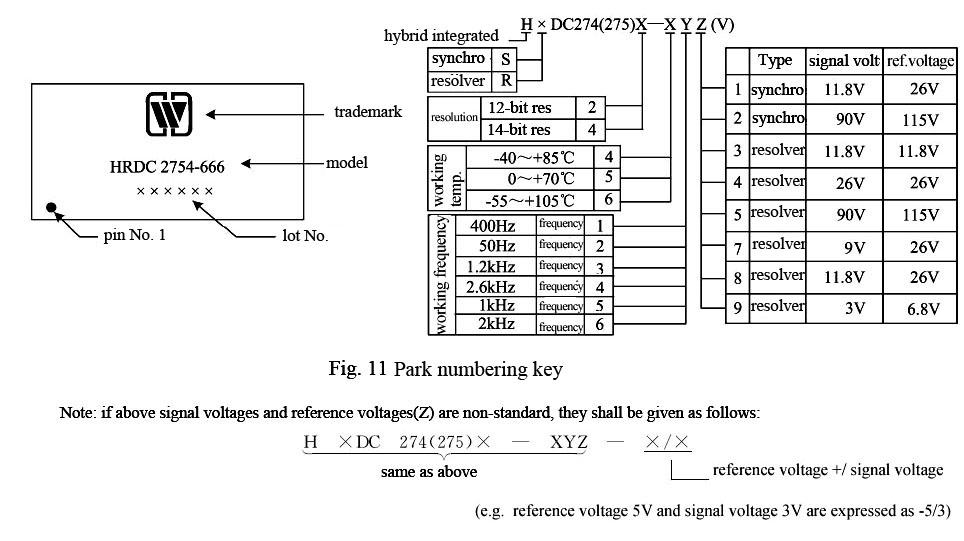

La puissance de fonctionnement adopte une alimentation CC de ± 15 V et + 5 V. Il existe deux types de signal de sortie : synchro à trois lignes et signal de référence (convertisseur SDC) ou résolveur à quatre lignes et signal de référence (convertisseur RDC) ; la sortie adopte des codes numériques parallèles du système binaire.

| Résolution : 12 bits, 14 bits |  |

| Vitesse de suivi élevée | |

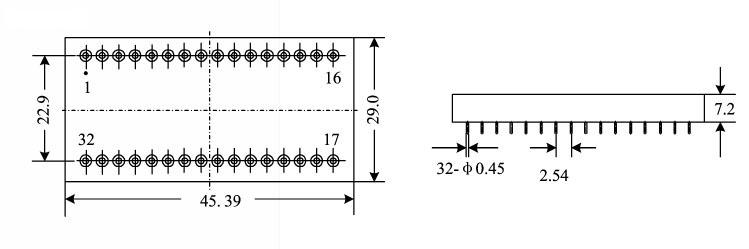

| Intégration hybride, boîtier métallique | |

| Sortie de verrouillage à trois états | |

| Avec signal de vitesse Vel sortie | |

| Compatibilité indéfinie avec la série AD1740 |

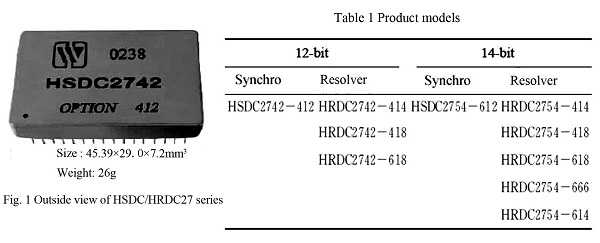

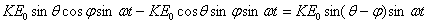

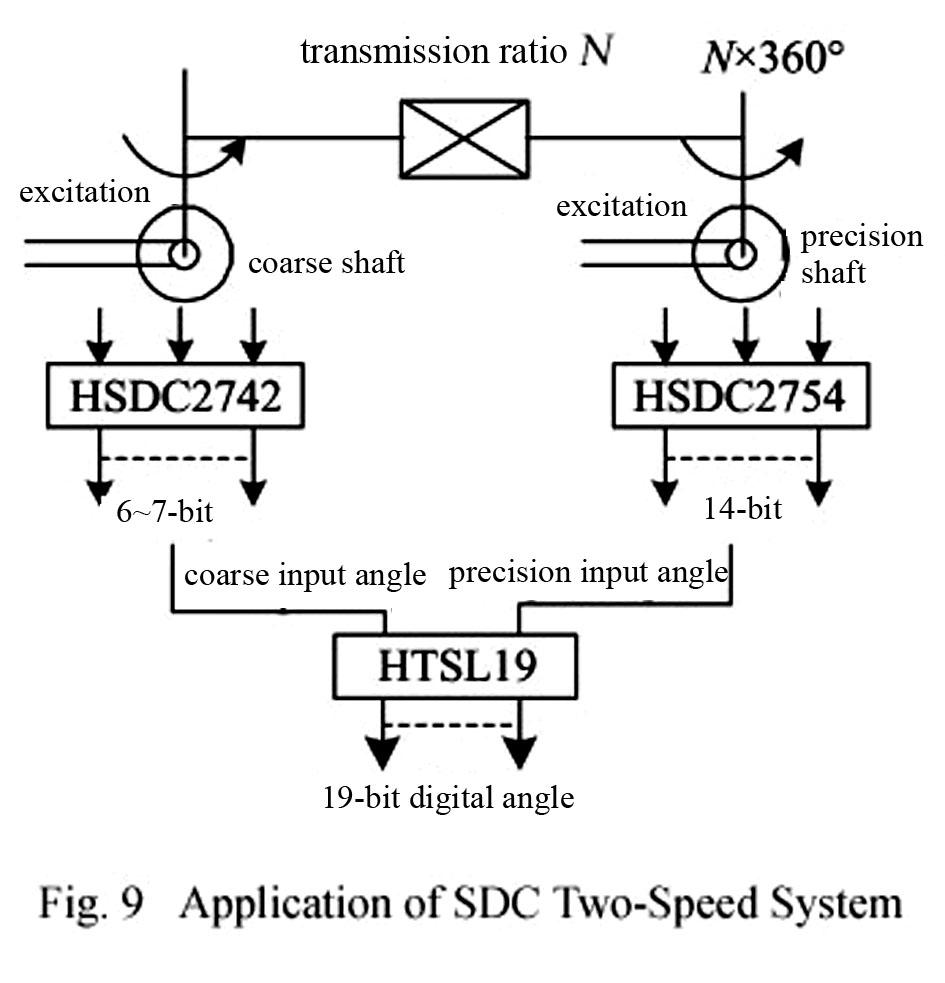

La série HSDC/HRDC27 est le convertisseur numérique vers synchro ou le résolveur vers les convertisseurs numériques pour le suivi continu de la boucle d'asservissement de type II. paquet, présente les avantages d'un petit volume, d'un poids léger et d'une grande fiabilité, etc., il est largement appliqué dans des systèmes de contrôle automatique tels que le système radar, le système de navigation, etc.

La puissance de fonctionnement adopte une alimentation CC de ± 15 V et + 5 V. Il existe deux types de signal de sortie : synchro à trois lignes et signal de référence (convertisseur SDC) ou résolveur à quatre lignes et signal de référence (convertisseur RDC) ; la sortie adopte des codes numériques parallèles du système binaire.

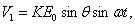

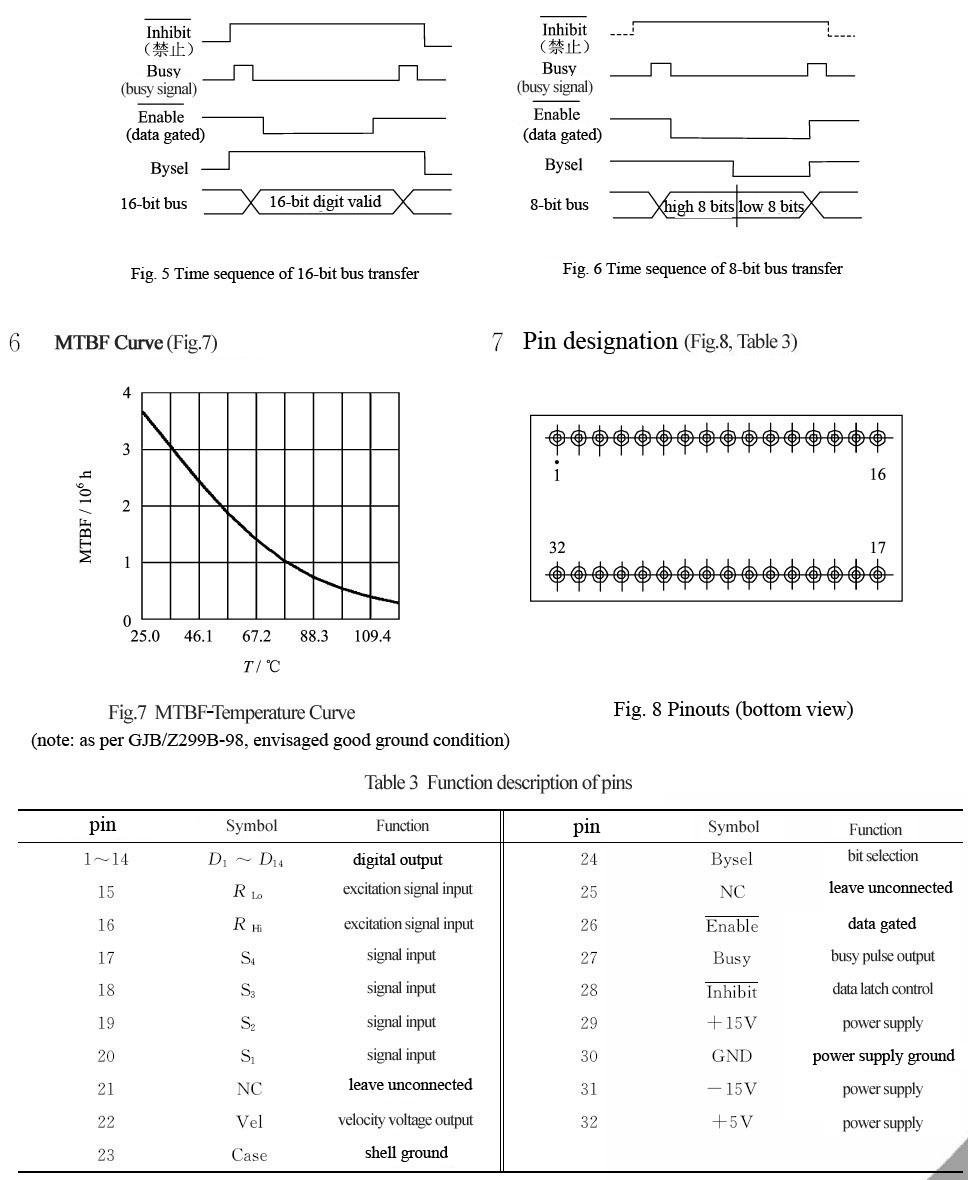

Tableau 2 Conditions évaluées et conditions de fonctionnement recommandées

Max. valeur nominale | Tension d'alimentation Vs : ± 17,5 V |

Tension logique VL : +5,5 V | |

Plage de température de stockage : -55℃~+125℃ | |

Conditions de fonctionnement recommandées | Tension d'alimentation Vs : ± 5 V |

Tension logique VL : 5 V | |

Valeur efficace de la tension de référence VRef : ±10 % de la valeur nominale | |

Validité de la tension de signal V1* : ±5 % de la valeur nominale | |

Fréquence de référence f* : 50 Hz à 2,6 kHz | |

Plage de température de fonctionnement TA : -40 ~ + 85 ℃, -55 ~ + 105 ℃ |

Remarque : * indique qu'il peut être personnalisé selon les exigences de l'utilisateur.

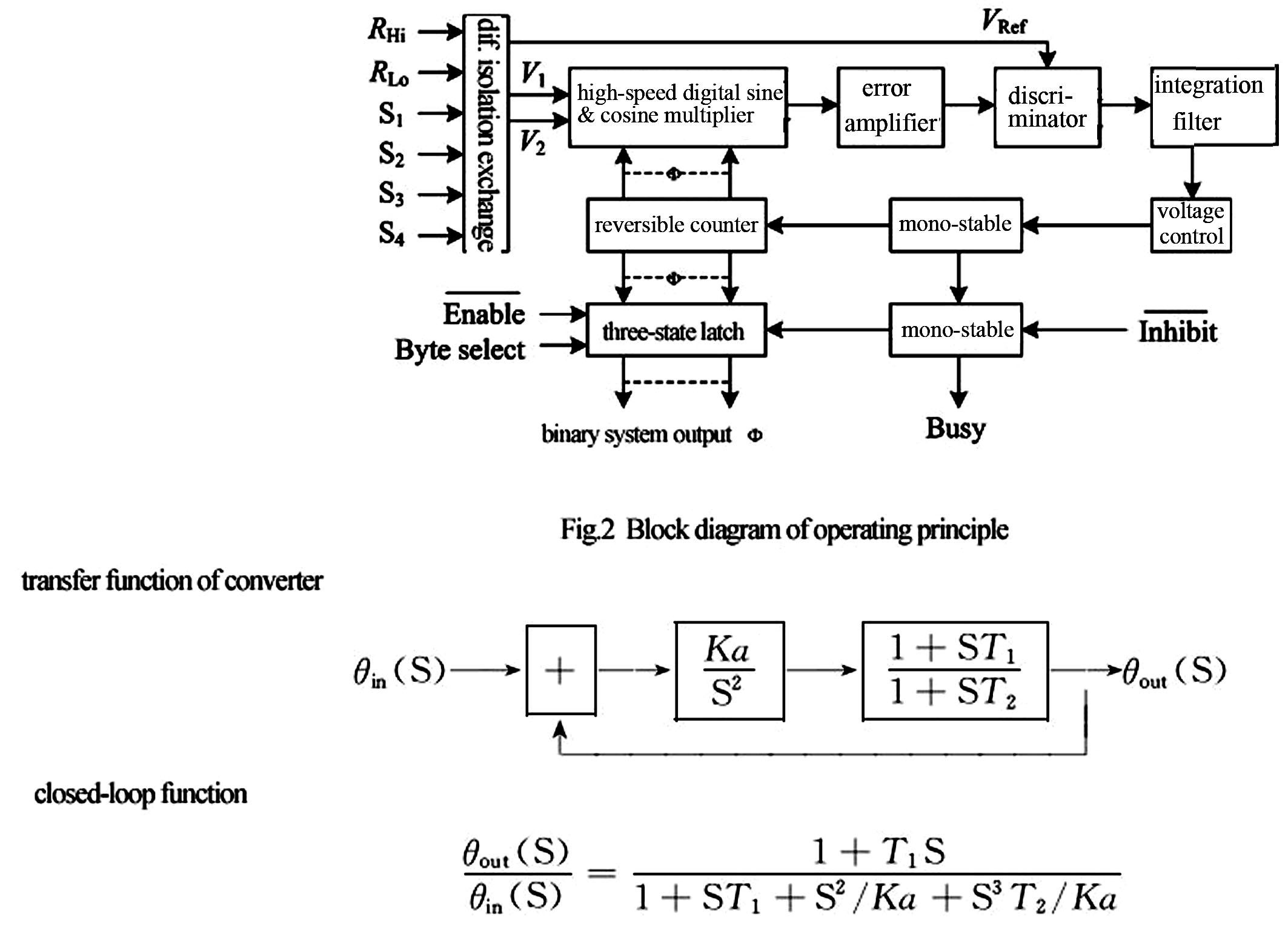

| production; lire des données 12 bits ou 14 bits ; réglez Inhibit sur "1" logique de manière à |  |

| transfert 16 bits). | B: le convertisseur est connecté au bus 8 bits, les bits D1 ~ D8 sont connectés au bus de données et les autres sont vides. |

| |

| La valeur Inhiber est | |

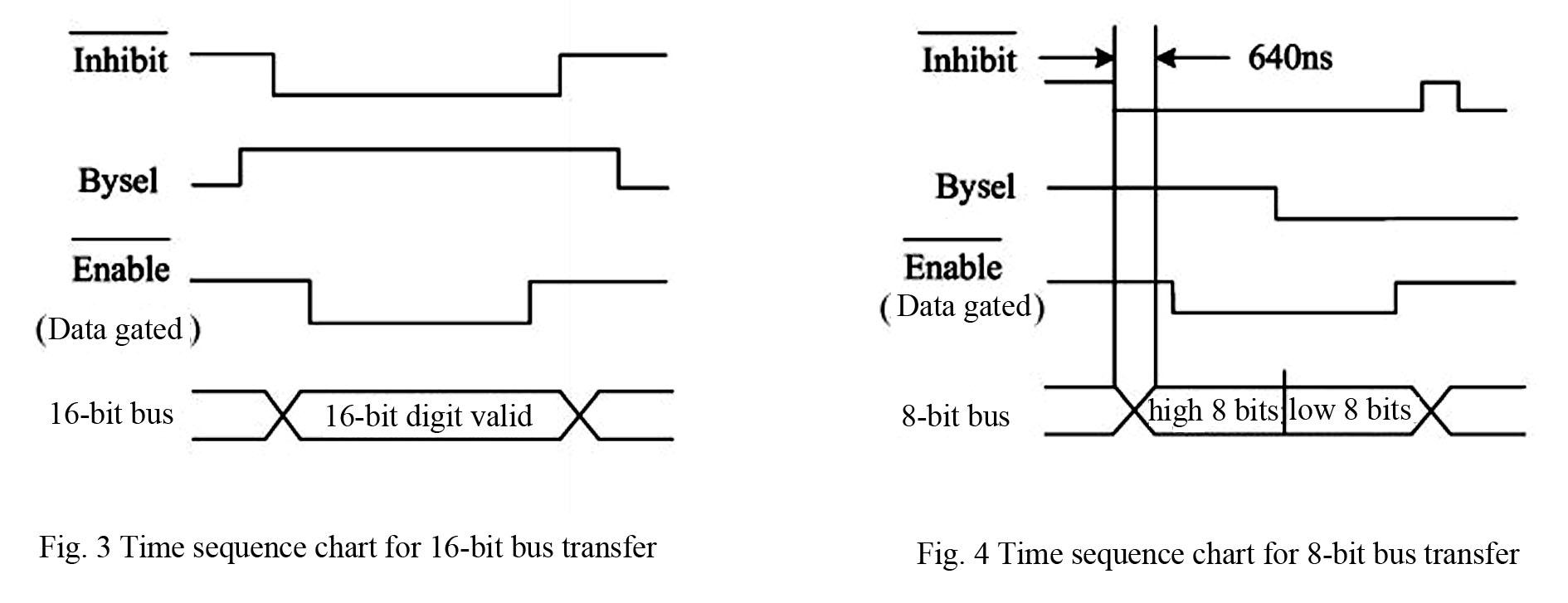

| Activer à la logique "0", les données de verrouillage à l'intérieur du convertisseur sont autorisées à | être sortie ; si Byse1 est réglé sur "1" logique, le convertisseur lit directement | les données 8 bits supérieures, si Byse1 est réglé sur "0" logique, le convertisseur lit | les bits restants, ajoute automatiquement zéro pour les bits incomplets ; régler la commande de verrouillage des données d'inhibition (signal d'inhibition) sur "1" logique afin de se préparer à la lecture des données valides suivantes (voir Fig. 3 et Fig. 4 pour la séquence de temps de transfert de 8 bits) | (2) Méthode Busy (lecture asynchrone) : | En mode de lecture asynchrone, l'inhibition de la commande de verrouillage des données (signal d'inhibition) est définie sur "1" logique ou vide, que la boucle interne soit toujours en | l'état stable ou si les données de sortie sont valides doivent être déterminés | à travers l'état du signal occupé Occupé. Lorsque le signal occupé est au niveau haut | niveau, il indique que les données sont en cours de conversion, et les données à ce |

| le temps est instable et invalide ; lorsque le signal d'occupation est au niveau bas, il | indique que la conversion des données est terminée et que les données à ce stade | Au | le temps est stable et valide. Une fois que le niveau haut apparaît dans Occupé pendant la lecture, | Au | la lecture de ce temps est invalide. En mode de lecture asynchrone, Occupé | Au | la sortie est un train d'impulsions de niveau TTL, la largeur entre est liée à | vitesse rotationnelle. De même, il existe également deux utilisations 8 bits et 16 bits |

X

X