| Conversion de l'isolation différentielle interne |  |

| Résolution 16 bits | |

| Précision : 2 minutes angulaires | |

| Sortie de verrouillage à trois états | |

| Vitesse de suivi continue élevée | |

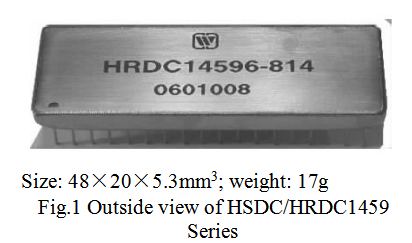

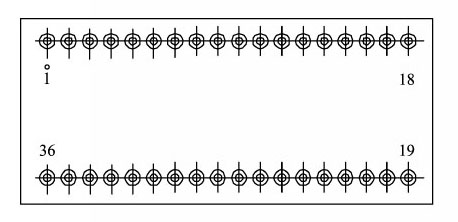

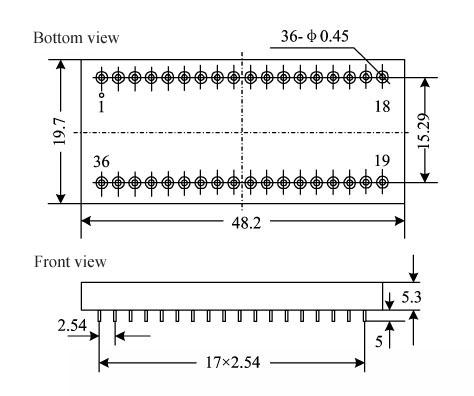

| Boîtier DDIP scellé en métal à 36 fils résistant au brouillard salin | |

| Compatible Pin-To-Pin avec le modèle SDC14560 de la société DDC |

| dispositif de conversion intégré pour un suivi continu conçu sur le | principe du servo modèle II. Les produits de cette série sont conçus et |

| fabriqués par le procédé MCM, les éléments centraux adoptent une puce spéciale | |

| développé indépendamment par notre institut. La disposition des broches est | |

| compatible avec les produits de la série SDC14560 de la société américaine DDC, 16 bits | |

| sortie de verrouillage de données de code binaire naturel parallèle, DIP 36 lignes totalement | |

| emballage métallique scellé, ont les avantages de haute précision, petit | |

| volume, faible consommation d'énergie, poids léger et haute fiabilité, etc., | et peut être largement utilisé dans des armes stratégiques et tactiques importantes telles que |

| avion, navire de guerre, canon, missile, radar, char, etc. | |

| 4. Performances électriques (tableau 1, tableau 2) | |

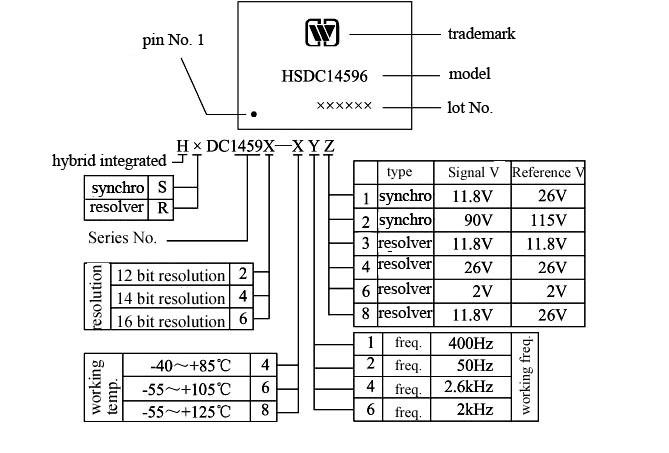

| Convertisseurs synchro-numériques ou convertisseurs résolveur-numérique (séries HSDC/HRDC1459) | |

| Tableau 1 Conditions nominales et conditions de fonctionnement recommandées | |

| Max. valeur nominale |

| Tension de signal V1 : valeur nominale ± 20 % | Tension de référence VRef : valeur nominale ± 20 % | Fréquence de fonctionnement f : valeur nominale ± 20 % | |

| Température de stockage Tstg : -65 ~ 150 ℃ | Conditions de fonctionnement recommandées | ||

| Tension d'alimentation logique VL : 5±0,5 V | Tension d'alimentation Vs : 15± 0,75 V | ||

| Tension de signal V1 : valeur nominale ± 10 % | Tension de référence VRef : valeur nominale ± 20 % | Fréquence de fonctionnement f : valeur nominale ± 20 % | — |

| Plage de température de fonctionnement (TA) : -55℃~125℃ | Remarque : * indique qu'il peut être personnalisé selon les besoins de l'utilisateur. | Tableau 2 Caractéristiques électriques | Paramètre |

| Conditions | — | Série HSDC14569 | (VSu003d15 V, VLu003d+5 V) |

| Norme militaire (Q/HW20725-2006) | — | 2V | Min. |

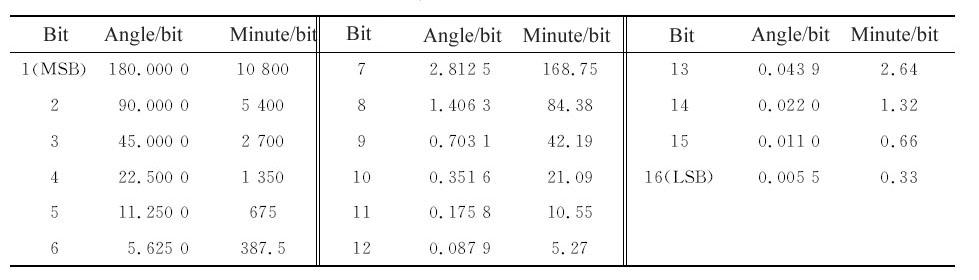

| Max. | — | Résolution | Code numérique parallèle du système binaire |

| 16 bits | — | 2V | Précision |

| ± 10 % de la tension du signal, la tension de référence et la plage de fluctuation de la fréquence de fonctionnement | — | -2 minutes angulaires | +2 minutes angulaires |

| Plage de fréquence de référence | — | 50Hz | 2600Hz |

| Plage de tension de référence | — | 115V | Impédance d'entrée de référence |

4.4kΩ 4.4kΩ | — | 0 | 129,2 kΩ |

Plage de tension de signal Plage de tension de signal | — | 0 | 90V |

Impédance d'entrée du signal Impédance d'entrée du signal | — | 0 | 4.4kΩ |

| 102,2 kΩ | — | Déphasage signal/référence | —70° |

| +70° | — | Niveau logique d'entrée | "1" logique ≥3,3 V |

| "0" logique ≤0,8 V | — | saisir | 0.8V |

| saisir | — | 0.8V | |

| saisir | — | — | 0.8V |

| Niveau logique de sortie | — | — | "1" logique ≥3,3 V |

| "0" logique ≤0,8 V | — | — | Sortie de code d'angle numérique |

| "1" logique ≥3,3 V | — | — | "0" logique ≤0,8 V |

| Conversion de la sortie du signal d'occupation (CB) | — | 200ns | 600ns |

| Sortie de bit de détection de défaut | La logique "0" indique un défaut | — | Capacité de chargement |

| 3TTL | Vitesse de suivi | ||

| 2.5rps | Constante d'accélération | ||

| +10V Courant VSu003d+15V 10mA |  VS u003d—15 V |

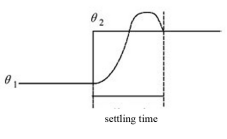

la vitesse. Le processus d'oscillation de l'angle numérique de sortie est illustré dans

la vitesse. Le processus d'oscillation de l'angle numérique de sortie est illustré dans 6. Principe de fonctionnement (Fig. 3)

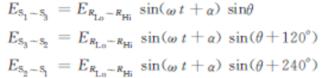

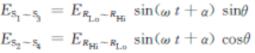

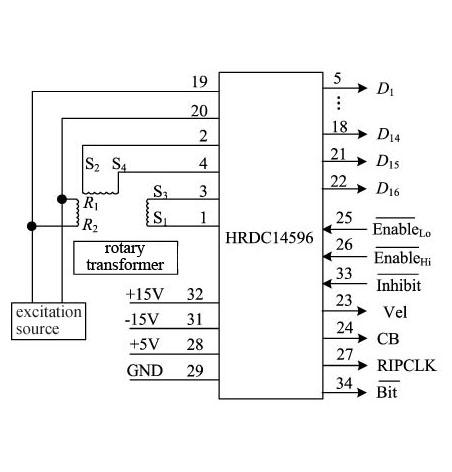

6. Principe de fonctionnement (Fig. 3)| Convertisseurs synchro-numériques ou convertisseurs résolveur-numérique (séries HSDC/HRDC1459) Le signal d'entrée de synchronisation (ou résolveur) est converti en signal orthogonal par l'isolement différentiel interne : | |

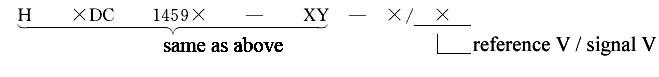

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofOù, θ est l'angle d'entrée analogique. Fig.2 Courbe de réponse échelonnée | Ces deux signaux et l'angle numérique φ du compteur interne réversibleof sont multipliés dans le multiplicateur des fonctions sinus et cosinus et sont erreur traitée : |

| amplification, discrimination de phase et filtration d'intégration, si | θ-φ≠0, l'oscillateur commandé en tension produira les impulsions, et le | compteur réversible compte, jusqu'à ce que θ-φ devienne zéro dans la précision de | le convertisseur, au cours de ce processus, la conversion suit le changement de | angle d'entrée tout le temps. | Méthode de lecture : |

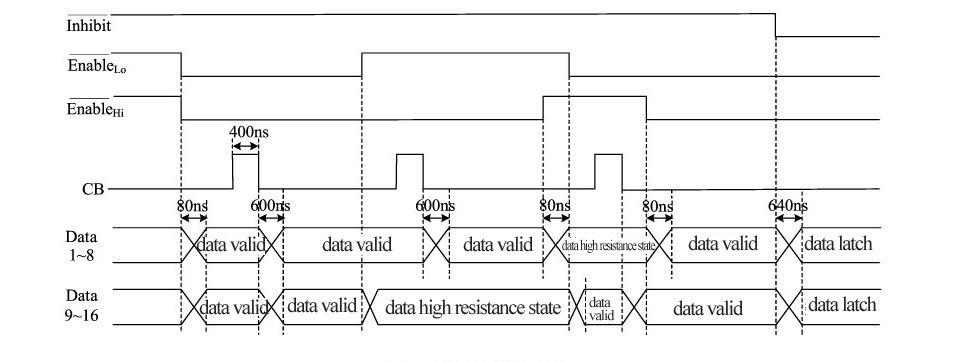

| 1 | S1 | Les deux méthodes suivantes sont disponibles pour le transfert de données : | 25 |  | (1) Méthode d'inhibition : |

| 2 | S2 | Après 640ns de | 26 |  | logique bas, les données de sortie sont valides et le convertisseur réalise le transfert de données via |

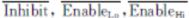

| 3 | S3 | et | 27 | . Une fois l'inhibition désactivée, le système génère automatiquement une impulsion d'une largeur égale à l'impulsion d'occupation pour la mise à jour des données. | (2) Mode buste : |

| 4 | S4 | Au bord montant de l'impulsion d'occupation, le compteur réversible à trois états compte ; au bord descendant de l'impulsion d'occupation, il génère en interne une impulsion de verrouillage d'une largeur égale à l'impulsion d'occupation pour mettre à jour les données du verrouillage à trois états, la séquence temporelle de transfert de données est illustrée à la Fig.4, en d'autres termes, après 600 ns de Logique d'occupation faible, le transfert stable de données est valide. En mode de lecture asynchrone, la sortie Occupé est un train d'impulsions de niveau CMOS. La largeur de son niveau haut et bas dépend de la fréquence de fonctionnement et de la vitesse de rotation de l'appareil sélectionné. | 28 | VL | Fig.4 Séquence temporelle du transfert de données |

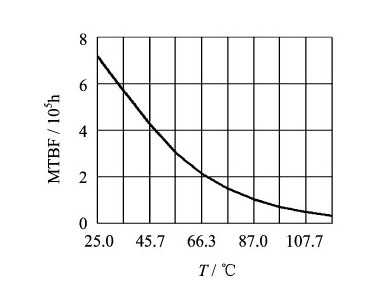

| 7. Courbe MTBF (Fig.5) | Convertisseurs synchro-numériques ou convertisseurs résolveur-numérique (séries HSDC/HRDC1459) | Fig.5 Courbe de température MTBF | 29 | 8. Désignation des broches (Fig.6, Table 3) | Convertisseurs synchro-numériques ou convertisseurs résolveur-numérique (séries HSDC/HRDC1459) |

| 19 | Fig.6 Désignation de la broche (Vue de bas) | (Remarque : selon GJB/Z299B-98, bon état du sol envisagé) | 30 | NC | Tableau 3 Désignation de la broche |

| 20 | RL | Broche | 31 | Symbole | Sens |

| 21 | Broche | Symbole | 32 | VS | Sens |

| 22 | Entrée S1 du résolveur (ou entrée synchro S1) | Contrôle numérique activé des 8 bits inférieurs | 33 | Entrée S2 du résolveur (ou entrée synchro S2) | Contrôle numérique activé des 8 bits supérieurs |

| 23 | Entrée résolveur S3 (ou entrée synchro S3) | RIPCLK | 34 | Sortie de signal zéro bit | Entrée du résolveur S4 (laisser non connecté) |

| 24 | CB | Alimentation +5 V | 5月18日 | NC | D1-D14 |

| Sortie numérique 1(MSB)-14 | Terre |

| Sol | RHi |

| Entrée de signal de référence haut de gamme | Pas de connection |

| RL | Entrée du signal de référence bas de gamme |

-VS

-VS -Alimentation 15 V

-Alimentation 15 V

D15 Sortie numérique 15

Sortie numérique 15 ).

).

Alimentation +15 V

D16

Sortie numérique 16 (LSB)

Inhiber

Entrée de signal statique

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Entrée du signal de référence bas de gammeofPlus bas | Entrée de signal activée par chiffre 8 bits, cette broche est la broche d'entrée logique deofcontrôle de blocage des données, sa fonction est d'effectuer un contrôle à trois états |

|  |

| en externe sur les données de sortie 8 bits inférieures du convertisseur. Le niveau bas est | valide, les données de sortie 8 bits inférieures du convertisseur occupent les données |

état de résistance, et l'appareil n'occupe pas le bus de données. Permettreet le temps de retard de libération est de 600ns (max). | plus haut | Entrée de signal activée par chiffre 8 bits, cette broche est la broche d'entrée logique de | contrôle de blocage des données, sa fonction est d'effectuer un contrôle à trois états | en externe sur les données de sortie 8 bits supérieures du convertisseur. Niveau faible | est valide, les données de sortie 8 bits supérieures du convertisseur occupent labus de données; Au niveau haut, la broche des données de sortie 8 bits supérieures est en haut | état de résistance, et l'appareil n'occupe pas le bus de données. Permettre | et le temps de retard de libération est de 600ns (max). | Inhiber l'électricité statique |

entrée de signal, cette broche est la broche d'entrée de la logique de commande, sa fonction | est de sortir des données en externe vers le convertisseur pour réaliser en option | Niverrouillage ou commande de dérivation. Au niveau haut, les données de sortie du | le convertisseur sort directement sans verrouillage ; à bas niveau, la sortie | les données du convertisseur sont verrouillées, les données ne sont pas mises à jour, mais lela boucle interne n'est pas interrompue, et le suivi fonctionne tous les | temps, Inhibit a connecté une résistance de pull-up en interne. Après 600ns (max) de retard de | Au front descendant du signal statique, les données deviennent stables (que le | l'appareil occupe le bus de données, c'est-à-dire quand sort-il les données dépendsur l'état de | etSortie de signal CB "occupé", ce signal indique si le code binaire |

X

X